# Simulation and Analysis of Symmetric Seven-level CMLI using Multicarrier SPWM Technique with Reducing Number of Switches

# K.Sridhar<sup>1,</sup> R.Prakash<sup>2</sup>, M.Valan Rajkumar<sup>3</sup>

<sup>1, 3</sup> Department of EEE, Gnanamani College of Technology, Namakkal-637018, Tamilnadu, India <sup>2</sup> Department of EEE, Vivekanandha College of Engineering for Women, Namakkal-637205, Tamilnadu, India

## ABSTRACT

This paper presents the simulation and analysis of symmetric seven-level cascaded multilevel inverter (CMLI) using multicarrier sinusoidal pulse width modulation (MC-SPWM) technique with reducing number of switches. The ultimate aim of the paper is, a renewed seven-level inverter topology is introduced incorporating the least number of unidirectional switches and gate trigger circuitry, thereby ensuring the minimum switching losses, reducing size and installation cost. The new proposed topology is well suited for drives and renewable energy applications. The performance quality in terms of total harmonic distortion (THD) and switching losses of the new CMLI is compared with conventional cascaded inverter and other existing seven-level reduced switch topologies using carrier-based pulse width modulation (PWM) techniques. The effectiveness of the proposed system is proved with the help of simulation. The simulation is performed in MATLAB/Simulink. From the simulation results, it shows that the proposed multilevel inverter works properly to generate the multilevel output waveform with minimum number of semiconductor devices and to achieve high dynamic performance with low THD. Keywords: Multilevel Inverter (MLI), Cascaded Multilevel Inverter (CMLI), Pulse Width Modulation (PWM), Multicarrier Sinusoidal Pulse Width Modulation (MC-SPWM), Total Harmonic Distortion (THD)

Date of Submission: 11-11-2017

Date of acceptance: 28-11-2017

\_\_\_\_\_

### I. INTRODUCTION

Due to environmental problems and lack of fossil fuels, use of renewable energy is increasing day by day. The power electronic converter's cost, power quality, efficiency space and reliability are the main key factor to integrate converter with renewable energy like solar energy, wind energy etc. The term "Multilevel Inverter" (MLI) was rooted years ago. Multilevel inverters offer various applications in voltage ranging from medium to high such as in renewable sources, industrial drives, laminators, blowers, fans, and conveyors. Small voltage step results in making the MLI withstand better voltage, fewer harmonics, high electromagnetic compatibility, reduced switching loss, and better power quality [1-10]. Cascaded multilevel inverters were developed in the initial stage. Later, diode-clamped MLI'S were developed followed by flying capacitor MLI'S. These three topologies utilize different mechanisms to produce the required output. The topology introduced first, that is, the CMLI, is simply series connection of H-bridges. The diode-clamped MLI uses series capacitor bank whereas, in flying capacitor MLI, floating capacitors are used in order to clamp the output voltage. H-bridge inverters have isolation transformers, and then H-bridge cascaded MLI'S were introduced to separate DC input sources. But they do not need either clamping a diode or flying capacitors. Absence of voltage imbalance is the main advantage of cascaded MLI. Fewer components are used in CMLI compared to diode-clamped and flying capacitor MLI [11-18]. Most of the researches are carried out in cascaded MLI configuration. But still the new trends are involved in the evolution of renewed multilevel inverters. Modifications are made in its inbuilt structure. To increase the power quality, first three-level multilevel inverter has been reported initially and with the significant changes in the converter topology, MLI can be categorized into three categories (i) symmetrical MLI, (ii) asymmetrical MLI (iii) S-DCMI. The first two types of topologies use more than one DC source and more number of switching devices viz. MOSFET, IGBT etc to increase the number of levels in output voltage. The fifty teen-level multilevel inverter using series and parallel DC sources is used to increase the number of levels by using H-bridge and eleven semiconductor switches [19-29].

A new concept of additive or subtractive combination of different DC sources based multilevel inverter has six unidirectional semiconductor switches and two bidirectional semiconductor switches to generate twenty seven output voltage levels using three DC sources. The demerit of this multilevel inverter is that it constitutes bidirectional semiconductor switches, which further enhance the number of switches, switching and conduction losses in comparison to the unidirectional device. Additionally, a five-level multilevel inverter using addition or subtraction principle of different DC sources is compared with conventional five-level inverter. A symmetrical inverter has been implemented comprising three main parts of an inverter as DC sources, main switches and one H-bridge cell using bidirectional switches [30-45].

The main objective of this inverter has been to reduce the number of switches, losses, installation area and cost with application as dynamic voltage restorer for improving power quality. Asymmetric and symmetric topologies are suggested to reduce the number of switching devices for specified number of output voltage levels. Three algorithms to select magnitude of different DC sources has been reported and implemented on optimal structure MLI. Cascaded cross-switched MLI topology is used as symmetric and asymmetric MLI. To reduce the switching losses, THD and to increase the efficiency a forty seven-level switch ladder MLI topology has been reported. This topology is used a multi winding transformer to create higher number of levels with H-bridge. To reduce the DC sources, cascade hybrid multilevel topology of asymmetric MLI has been reported which uses one H-bridge for each phase with a bottom three leg inverter. An optimal structure has been used to reduce the switches, DC sources, standing voltage and to maximize the number of levels [46-58].

A seven-level MLI was generated with nine switches reducing three switches from the main conventional CMLI. It offers good results yielding desired a seven-level output with low THD. A seven-level MLI with seven switches reducing two more switches from the previous topology made a far improvement in the investigation of the switch reduction. Yet another topology of seven-level MLI was configured with four dc sources and just six switches to get seven-level output. The latter made a drastic move in topology development since the THD is low, and gate circuits used to drive the switches are less [59-65].

It is mentioned everywhere that simplicity is the main advantage of CMLI to generate five-levels using eight switches, seven-levels with twelve switches, nine-levels with sixteen switches, and so on. It clearly reveals that an increase in levels demands more number of switches. Then the comment on simplicity of CMLI is simply contradictory. Hence, the focus was eyeing on a real solution to this problem, that is, how to simplify the complex circuit. Then arise the concept of "switch reduction". Exploring the existing topologies on basic seven-level, switch reduction was made from twelve switches to nine, gradually to seven and then to six.

Aiming at reducing the switches to the maximum possible extent and reducing complexity, the new topology is introduced with five switches for seven-levels, and this would be the least possible reduction. The new MLI configuration is made of five switches eliminating one switch from the existing six switches, seven-level topology in a special arrangement with four inputs DC sources to generate seven-level output. The fewer switches we use lessen the cost of circuit building. The circuit credibility is checked without using PWM. Then identifying the effectiveness in working simulated the circuit with phase disposition (PD), phase opposition disposition (APOD) using MATLAB/Simulink.

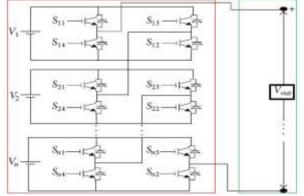

### II. CASCADED H-BRIDGE MULTILEVEL INVERTER TOPOLOGY

Using three DC voltage sources, three H-bridge units each with four switches together forming twelve switches in total are used in conventional CMLI which is represented in Fig 1. General expression for output voltage levels, m = (n+2)/2 where *m* is the number of switches in the configuration. Each Bridge is outputting three-levels, +Vdc, 0, -Vdc. The three-level CMLI consist of single H-bridge combine with a series of the power conversion cell. Cascaded H-bridge multilevel inverter is better than the diode clamped inverter and flying capacitors inverter, it requires less number of the component in each switching levels.

Fig. 1 Conventional cascaded n-level Multilevel Inverter

In cascade H-bridge multilevel inverter, the grouping of switches and capacitors is called H-bridge consisting of isolated DC Voltage source and cascading three Bridges in such a fashion to produce stepped seven-level staircase waveforms. In Existing CMLI Topology, seven-level, nine switches, this topology is built with three dc sources, one H-bridge composed of four switches and then additional five more switches for producing stepped seven-levels, for positive and negative half cycles. In seven-level, seven switches, this topology is made of seven switches and three dc sources. One H-bridge present in the topology is mainly for polarity change. Here, three switches conduct at a time for level generation. In seven-level, six switches, this is a special configuration consisting of four dc sources and six switches. One switch across the load is used for zero level.  $S_1$ ,  $S_2$ ,  $S_3$  used for level generation and  $S_4$ ,  $S_5$  switches for polarity changing.

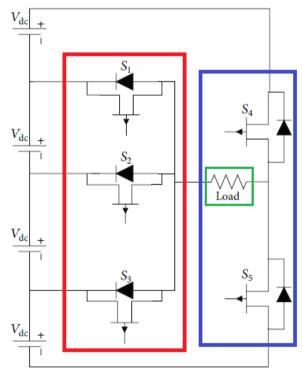

### III. PROPOSED FIVE-SWITCH CMLI TOPOLOGY

The proposed seven-level MLI as shown in Fig 2 is about redesigning of existing six switch topology eliminating one switch attaining the tag of five switch configuration. The circuit thus obtained is the simplest design compared to conventional and all other existing topologies. It consists of four dc sources of seven-levels, for nine-level, five dc sources and so on. Generalized expression for output voltage levels for the new topology proposed is  $m = (2 \times n-3)$ , where m = number of output voltage levels, n = number of switches  $m = (2 \times V-1)$ , where V = number of dc sources.

Fig. 2 Seven-level five-switch CMLI topology

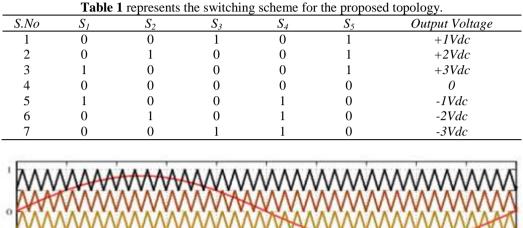

The design of pulse generation circuit makes the topology differ from others so as to obtain the unique pulse pattern to trigger the switches at the proper instant. Table 1 represents the switching scheme for the proposed topology. Switches  $S_1$ ,  $S_2$ , and  $S_3$  need to be compulsorily unidirectional or else the output waveform will get distorted. Reduced switches make the circuit compact and user-friendly. The usage of four dc sources for the generation of seven-level MLI results in less utilization of sources, switch reduction benefits in low switching losses. No H-Bridge is used. Just two switches play the role of polarity reversal.

### IV. METHODOLOGY AND PULSE GENERATION CIRCUIT

The pulse generation is essential in order to trigger the switches with appropriate pulse pattern to produce the desired seven-level output. It is inevitable to analyze which PWM suits the new topology. The simplest PWM technique is the carrier-based PWM technique. It can be further categorized into level and phase shifting carrier-based PWM, respectively. Since the phase shifting carrier-based PWM yields more harmonics comparatively, the level shifting carrier-based PWM is preferred over it. Therefore, the new circuit design is analyzed with level shifting carrier based PWMs, that is, PD, POD, and APOD PWMs. Interestingly, it is noted that POD gives lower THD and is found to be the apt PWM for proposed topology. The PWM generation circuit is the

### Simulation and Analysis of Symmetric Seven-level CMLI using Multicarrier SPWM Technique with ..

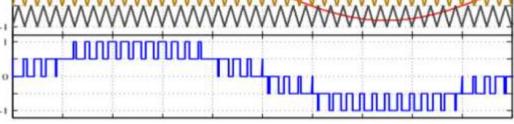

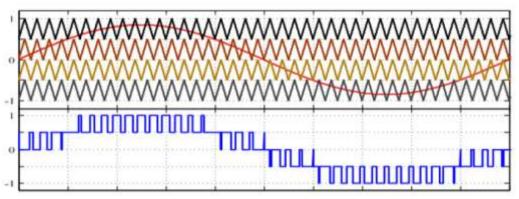

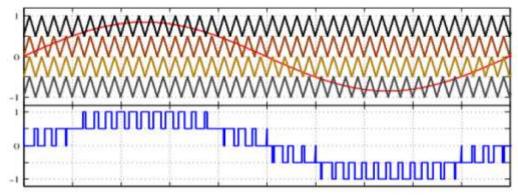

heart of the circuitry. One reference sine wave of amplitude 0.8 and frequency 50 Hertz is compared with  $C_1$  to  $C_6$  triangular carriers of frequency 1KHz. If *m*-level needs to be synthesized, (m-1) carriers are required. Whenever the reference sinusoid exceeds the carrier, instant pulses are generated to trigger the switch to '0' N-state. Higher triangular carrier amplitude is taken as one. The carrier alignment for the carrier based PWM technique is shown in following figures. The pulse waveform of carrier-based PWM techniques with phase disposition (PD)-PWM is shown in Fig 3. The pulse waveform of carrier-based PWM techniques with phase opposition disposition (POD)-PWM is shown in Fig 4.

Fig.3 Pulse waveform of carrier-based Phase disposition (PD)-PWM

Fig.4 Pulse waveform of carrier-based Phase Opposition Disposition (POD)-PWM

The pulse waveform of carrier-based PWM techniques with alternative phase opposition disposition (APOD)-PWM is shown in Fig 5. In PD or phase disposition technique, (m-1) carriers are aligned in the same direction/phase. In POD or phase opposition disposition for seven-level, six carriers are aligned as symmetric mirror images above and below the zero reference axis. In alternate phase opposition disposition, alternate carriers are in the same phase and neighboring carriers in the opposing phase. The reference signal comparing with carrier generating pulse which is then modified feeding to logic gates in order to get the required pattern to trigger the switches at the proper instant. For examples switch  $S_1$  needs to have a pulse so as to obtain +Vdc and -3Vdc and  $S_2$  require +2Vdc and -2Vdc.  $S_3$  conducts +3Vdc and -Vdc. Also, switches  $S_5$  and  $S_4$  conduct positive and negative half cycles, respectively.

Fig.5 Pulse waveform of carrier-based Alternative Phase Opposition Disposition (APOD)-PWM

## V. SIMULATION RESULTS AND DISCUSSION

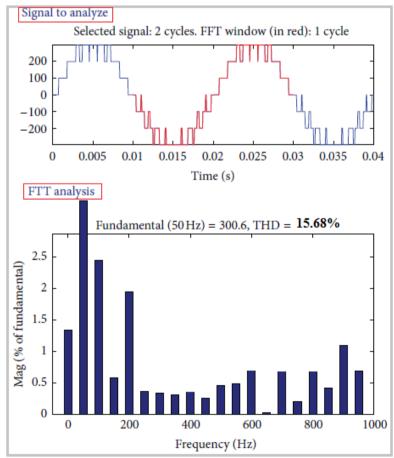

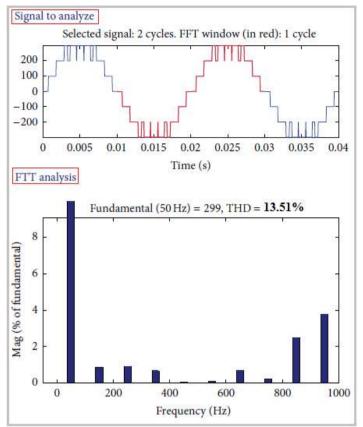

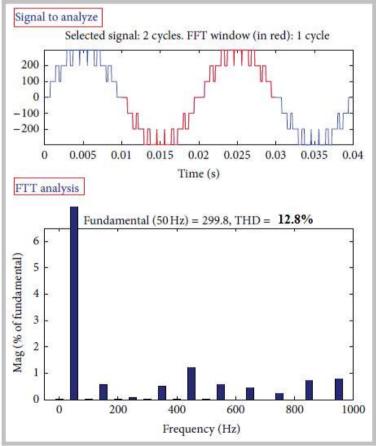

In the proposed seven-level MLI, the circuit is built of five MOSFET unidirectional switches. It can also be built with three unidirectional and two bidirectional switches. The load is resistive with a value of 10 ohms. Four 10-volt symmetric DC input voltages are used. Note that in order to obtain the shaped seven-level output without distortion, MOSFET block parameters in MATLAB should vary according to the load used. The FFT analysis of seven-level five-switch CMLI using carrier-based Phase disposition (PD)-PWM is shown in Fig 6. The FFT analysis of seven-level five-switch CMLI using carrier-based phase opposition disposition (POD)-PWM is shown in Fig 7. The FFT analysis of seven-level five-switch CMLI using carrier-based alternative phase opposition disposition (APOD)-PWM is shown in Fig 8.

Fig. 6 FFT analysis of seven-level five-switch CMLI using PD PWM.

Fig. 7 FFT analysis of seven-level five-switch CMLI using POD PWM.

Fig. 8 FFT analysis of seven-level five-switch CMLI using APOD PWM.

www.ijceronline.com

#### **VI. CONCLUSION**

This paper presents the simulation and analysis of symmetric seven-level cascaded multilevel inverter (CMLI) using multicarrier sinusoidal pulse width modulation (MC-SPWM) technique with reducing number of switches. The seven-level MLI using just five switches is successfully introduced simulating the circuitry using MATLAB/SIMULINK and observed a clear stepped seven-level waveform. It is found that the alternative phase opposition disposition PWM dominates all other PWMs in the proposed configuration. The validity of the proposed method is shown through extensive simulation investigations applied to symmetric seven-level cascaded multilevel inverter.

#### REFERENCES

- A. Chel, G.N. Tiwari, A. Chandra, Simplified method of sizing and life cycle cost assessment of buildings integrated photovoltaic system, Energy and Buildings 41 (2009) 1172-1180.

- F. Blaabjerg, Z. Chen, S. Kjaer, Power electronics as efficient interface in dispersed power generation systems, IEEE Transactions on Power Electronics 19 (2004) 1184-1194.

- [3] G. M. Master, Renewable and efficient electric power systems, A John Wiley & Sons, Inc., Publication, pp. 385-604, 2004.

- [4] R. Faranda and S. Leva, "Energy comparison of MPPT techniques for PV systems", WSEAS Trans. Power Syst., vol. 3, iss. 6, pp. 446-455, 2008.

- [5] Jose Rodriguez, Jih-Sheng Lai and Fang Zheng Peng "Multilevel Inverters: A Survey of Topologies, Controls, and Applications", IEEE transactions on industrial electronics, vol. 49, no. 4, pp. 724–738, august 2002

- [6] M. Schneider, L. Moran and J. Dixon, "An active power filter implemented with a three-level NPC voltage-source inverter", 28th Annual IEEE Power Electronics Specialists Conference (PESC'97), Volume 2, 22-27 Oct. 1997, Page(s):1121 - 1126.

- [7] Sun Hui, Zou Ji-yan and Li Wei-dong, "A novel active power filter using multilevel converter with self voltage balancing", IEEE Proceedings of International Conference on Power System Technology (PowerCon 2002), Volume 4, 13-17 Oct. 2002 Page(s):2275 - 2279.

- [8] Bin Wu, High-Power Converters and AC Drives, IEEE Press and Wiley, 2006, pp 143-176.

- [9] M.ValanRajkumar, P.S.Manoharan, Modeling and Simulation of Three-phase DCMLI using SVPWM for Photovoltaic System, Springer Lecture Notes in Electrical Engineering, under the volume titled "Power Electronics & Renewable Energy Systems", Volume 326, Chapter No 5, January 2015, Pages 39-45.

- [10] M.ValanRajkumar, P.S.Manoharan, Harmonic Reduction of Fuzzy PI Controller based Three-Phase Seven-level DCMLI with SVPWM for Grid Connected Photovoltaic System, Journal International Review on Modeling and Simulations, Volume 6, No 3, June 2013, Pages 684-692.

- O. Vodyakho, T. Kim, S. Kwak, C.S. Edrington, "Comparison of the space vector current controls for shunt active power Filters" IET Power Electron., 2009, Vol. 2, Iss. 6, pp. 653–664

- [12] A.Ravi, P.S.Manoharan, M.ValanRajkumar, "Harmonic Reduction of Three-Phase Multilevel Inverter for Grid connected Photovoltaic System using Closed Loop Switching Control", Journal-IREMOS, Volume 5, No 5, October 2012, Pages 1934-1942. ISSN: 1974-9821 (Print), 1974-982X (Online)

- [13] P.Thirumurugan, P.S.Manoharan, M.ValanRajkumar, "VLSI Based Inverter Switching Control" in the proceedings of International Conference on Mathematical Modeling and Applied Soft Computing MMASC'12 – Coimbatore Institute of Technology on July 2012, Vol-2 (Page):965-973.

- [14] C.Hemalatha, M.Valan Rajkumar, G.Vidhya Krishnan, "Simulation and Analysis for MPPT Control with Modified firefly algorithm for photovoltaic system", International Journal of Innovative Studies in Sciences and Engineering Technology, Volume 2, No 11, Nov.2016, Pages 48-52.

- [15] G.Vidhya Krishnan, M.Valan Rajkumar, C.Hemalatha, "Modeling and Simulation of 13-level Cascaded Hybrid Multilevel Inverter with less number of Switches", International Journal of Innovative Studies in Sciences and Engineering Technology, Volume 2, No 11, Nov.2016, Pages 43-47.

- [16] M.ValanRajkumar, P.S.Manoharan, FPGA Based Multilevel Cascaded Inverters with SVPWM Algorithm for Photovoltaic system, Elsevier Journal Solar Energy, Volume 87, Issue 1, January 2013, Pages 229-245.

- [17] M.ValanRajkumar, P.S.Manoharan, Space Vector Pulse Width Modulation of Three-Phase DCMLI with Neuro-Fuzzy MPPT for Photovoltaic System, World Journal of Modelling and Simulation, Volume 10, No 3, August 2014, Pages 193-205.

- [18] Mansour Mohseni, and Syed M. Islam, "A New Vector-Based Hysteresis Current Control Scheme for Three-Phase PWM Voltage-Source Inverters", IEEE Transactions on Power Systems, vol.25,No.9,September-2010.

- [19] M.Valan Rajkumar, Prakasam, P. and Manoharan, P.S. (2016) Investigational Validation of PV Based DCDMLI Using Simplified SVM Algorithm Utilizing FPGA Tied with Independent Sources. Circuits and Systems, Volume 7, No 11, 3831-3848. http://dx.doi.org/10.4236/cs.2016.711320

- [20] P.Thirumurugan, P.S.Manoharan, M.ValanRajkumar, VLSI Based Space Vector Pulse Width Modulation Switching Control in the proceedings of IEEE International Conference on Advanced Communication Control and Computing Technologies ICACCCT 2012 on August 2012, ISBN No. 978-1-4673-2045-0 (Print) (Page):366-370.

- [21] M.ValanRajkumar, P.S.Manoharan, "Modeling, Simulation and Harmonic Reduction of Three-Phase Multilevel Cascaded Inverters with SVPWM for Photovoltaic System", Journal International Review on Modeling and Simulations, Volume 6, No. 2, April 2013, Pages 342-350. ISSN: 1974-9821 (Print), 1974-982X (Online)

- [22] Carlos Henrique da Silva, Rondineli R. Pereira, Luiz Eduardo Borges da Silva, Germano Lambert-Torres, João Onofre Pereira Pinto, and Se Un Ahn, "Dead-Time Compensation in Shunt Active Power Filters Using Fast Feedback Loop" IEEE conference, 2008.

- [23] M.Valan Rajkumar, G.Ranjhitha, M.Pradeep, Mohammad Fasil PK, R.Sathishkumar, "Fuzzy based Speed Control of Brushless DC Motor fed Electric Vehicle", International Journal of Innovative Studies in Sciences and Engineering Technology (IJISSET), Volume: 3, Issue: 3, March 2017, Pages 12-17. ISSN: 2455-4863 (Online).

- [24] M.Valan Rajkumar, J.Chandramohan, D.Aravind, M.Basker, "Performances Analysis of Power Factor Correction for PWM Control based Bridgeless Cuk Rectifier with Positive Output Voltage", International Journal of Emerging Technologies in Engineering Research (IJETER), Volume: 5, Issue: 4, April 2017, Pages 116-121. ISSN: 2454-6410 (Online).

- [25] K.Aswini, K.Nandhini, SR.Nandhini, G.Akalya, B.Rajeshkumar, M.Valan Rajkumar, "Simulation and Analysis of ASCAD Multilevel Inverter with SPWM for Photovoltaic System", International Journal of Innovative Studies in Sciences and Engineering Technology (IJISSET), Volume: 3, Issue: 4, April 2017, Pages 1-9. ISSN: 2455-4863 (Online).

- [26] M.Valan Rajkumar, M.Mahakumar, M.Manojkumar, M.Hemaraj, E.Kumaravel, "Modelling and Analysis of DC-DC Converter with Various MPPT Algorithms for PV System", International Journal of Innovative Studies in Sciences and Engineering Technology (IJISSET), Volume: 3, Issue: 4, April 2017, Pages 17-22. ISSN: 2455-4863 (Online).

- [27] M.Valan Rajkumar, T.Indumathi, "Analysis of Low Power Multi-core Embedded Management for Energy Harvesting", IOSR-Journal of Electrical and Electronics Engineering, Volume 12, Issue 2, Ver. II, March-April 2017, Pages 25-33. ISSN: 2320-3331 (Print) 2278-1676 (Online).

- [28] A.Ravi, M.Valan Rajkumar, P.S.Manoharan, "Harmonic Reduction of Three-Phase Eleven-level DCMLI with Fuzzy MPPT for Grid Connected Photovoltaic System", International Journal of Applied Engineering Research (IJAER), Volume 10, No 2, 2015, Pages 3251-3268. ISSN: 0973-4562 (Print).

- [29] A. Masaoud, P. Hew Wooi, S. Mekhilef, and A. S. Taallah, "New Three- Phase Multilevel Inverter With Reduced Number of Power Electronic Components," Power Electronics, IEEE Transactions on, vol. 29, no. 11, pp. 6018-6029, 2014.

- [30] M.Valan Rajkumar, J.Karthikeyan, P.S.Manoharan, "Modeling and Simulation of Multiphase DCMLI with SVPWM for Photovoltaic System", International Journal of Applied Engineering Research (IJAER), Special Issue: Volume 9, No 24, 2014, Pages 8477-8483. ISSN: 0973-4562 (Print).

- [31] S. Yeongrack, and H. Jung-lk, "Direct Power Control of a Three-Phase Inverter for Grid Input Current Shaping of a Single-Phase Diode Rectifier With a Small DC-Link Capacitor," Power Electronics, IEEE Transactions on, vol. 30, no. 7, pp. 3794-3803, 2015.

- [32] M.ValanRajkumar, P.S.Manoharan, "Modeling and Simulation of Five-level Five-phase Voltage Source Inverter for Photovoltaic Systems", Journal PrzegladElektrotechniczny, Volume 10, No. 10, October 2013, Pages 237-241. ISSN: 0033-2097 (Print)

- [33] T. Ghennam, E. M. Berkouk, and B. Francois, "A Novel Space-Vector Current Control Based on Circular Hysteresis Areas of a Three-Phase Neutral-Point-Clamped Inverter," Industrial Electronics, IEEE Transactions on, vol. 57, no. 8, pp. 2669-2678, 2010.

- [34] M.Valan Rajkumar, P.S.Manoharan, A.Ravi, "Simulation and an Experimental Investigation of SVPWM Technique on a Multilevel Voltage Source Inverter for Photovoltaic Systems", Elsevier International Journal of Electrical Power and Energy Systems, Volume 52, Issue 9, November 2013, Pages 116-131. ISSN: 0142-0615 (Print), 1879-3517 (Online)

- [35] SR.Nandhini, G.Akalya, K.Aswini, K.Nandhini, M.Valan Rajkumar, B.Rajeshkumar, "A New Topology of H-bridge based Multilevel Inverter for PV System with Reduced Switches", International Journal of Emerging Technologies in Engineering Research (IJETER), Volume: 5, Issue: 4, April 2017, Pages 60-68. ISSN: 2454-6410 (Online).

- [36] M.Valan Rajkumar, M.Mahakumar, M.Manojkumar, M.Hemaraj, E.Kumaravel, "A New DC-DC Converter Topology with Grey Wolf MPPT Algorithm for Photovoltaic System", International Journal of Emerging Technologies in Engineering Research (IJETER), Volume: 5, Issue: 4, April 2017, Pages 54-59. ISSN: 2454-6410 (Online).

- [37] L.Malliga, K.Bommannaraja, M.Valan Rajkumar, "Investigation of FCM based Image Retrievel-Segmentation on Human Computational Intelligent Systems", International Journal of Applied Engineering Research (IJAER), Special Issue: Volume 10, No 12, 2015, Pages 10769-10774. ISSN: 0973-4562 (Print).

- [38] U.Suresh Kumar, P.S.Manoharan, M.Valan Rajkumar, "Feasibility Sensitivity Analysis in Potential Area for Standalone Hybrid Renewable Energy in Tamil Nadu, India", Applied Mechanics and Materials Journal, under the volume titled "Advancements in Automation and Control Technologies", Volume 573, June 2014, Pages 757-766. ISSN: 1660-9336 (Print), ISBN-13: 978-3-03835-124-5 (Online).

- [39] C.Hemalatha, M.Valan Rajkumar, M.Gayathri, "IOT Based Building Monitoring System Using GSM Technique", IOSR-Journal of Electronics and Communication Engineering (IOSR-JECE), Volume 12, Issue 2, Ver. III, March-April 2017, Pages 68-75. ISSN: 2278-8735 (Print) 2278-2834 (Online).

- [40] S.Rashini, P.S.Manoharan, M.Valan Rajkumar, "Interfacing PV system to the Utility Grid using a Voltage Source Inverter", Journal of Emerging Technologies Electrical Engineering, Special Issue- ICBDM 2013, Volume 1, No 1, March 2013, Pages 124-129. ISSN: 0973-2993 (Print)

- [41] S.Sathyaraj, M.Valan Rajkumar, J.Chandramohan, "Modeling and Simulation of Asymmetric Cascaded Multilevel Inverter with Reduced Switches using Multicarrier PWM Control", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering (IJAREEIE), Volume 5, Issue 10, October 2016, Pages 8064-8071. ISSN: 2320-3765 (Print), 2278-8875 (Online)

- [42] G.Ranjhitha, M.Valan Rajkumar, "Implementation of Genetic Algorithm based Maximum Power Point Tracking for Photovoltaic System", International Journal of Innovative Research in Science, Engineering and Technology (IJIRSET), Volume 5, Issue 11, November 2016, Pages 18860-18868. ISSN: 2347-6710 (Print), 2319-8753 (Online)

- [43] S.Sathishkumar, M.Valan Rajkumar, R.Yuvaraj, "Modeling and Analysis of Soft-Switched Interleaved Boost Converter for Photovoltaic System", International Journal for Science and Advance Research in Technology (IJSART), Volume 2, Issue 11, November 2016, Pages 43-48. ISSN: 2395-1052 (Online)

- [44] M.Sundaraperumal, M.Valan Rajkumar, A.Venkatesh, "Modeling and Analysis of Current Source Multilevel Inverter using PI Controllers with Multicarrier PWM Technique", International Journal for Science and Advance Research in Technology (IJSART), Volume 2, Issue 11, November 2016, Pages 275-280. ISSN: 2395-1052 (Online)

- [45] R. Yuvaraj, S. Sathishkumar, M. Valan Rajkumar, "Analysis of PV based Soft Switching Boost DC-DC Converter with Zero Current Switching Technique", International Journal of Advanced Research in Management, Architecture, Technology and Engineering (IJARMATE), Volume 2, Issue 12, December 2016 Pages 1-5. ISSN: 2454-9762 (Print) 2454-9762 (Online)

- [46] M.Valan Rajkumar, M.Mahakumar, M.Manojkumar, M.Hemaraj, E.Kumaravel, "A New MPPT design using Grey Wolf Optimization Techniques with DC-DC Converter for PV System", International Journal for Science and Advance Research in Technology (IJSART), Volume 3, Issue 3, March 2017, Pages 829-835. ISSN: 2395-1052 (Online)

- [47] K.Nandhini, SR.Nandhini, G.Akalya, K.Aswini, M.Valan Rajkumar, B.Rajeshkumar, "Implementation of 21-level Asymmetrical Cascaded Multilevel Inverter with Reducing Number of Switches", International Journal for Science and Advance Research in Technology (IJSART), Volume 3, Issue 3, March 2017, Pages 809-818. ISSN: 2395-1052 (Online)

- [48] S.Sathishkumar, M.Valan Rajkumar, S.Vinothkumar, M.Maruthamuthu, A.Sounder, A.Kumaresan, "A New Design for DC-DC Converter Topology with MISO for Renewable Energy Resources", International Journal of Emerging Technologies in Engineering Research (IJETER), Volume: 5, Issue: 4, April 2017, Pages 143-149. ISSN: 2454-6410 (Online)

- [49] M.Valan Rajkumar, M.Mahakumar, M.Manojkumar, M.Hemaraj, E.Kumaravel, "Implementation of Various MPPT Algorithms with SEPIC Converter for PV System", International Journal of Engineering Research & Technology-Special Issue 2017, Volume 5, Issue 13, 2017, Pages 589-593. ISSN: 2278-0181 (Print)

- [50] G.Akalya, K.Aswini, K.Nandhini, SR.Nandhini, M.Valan Rajkumar, B.Rajeshkumar, "Modelling and Analysis of Multilevel Inverter for Photovoltaic System", International Journal of Advanced Research Methodology in Engineering & Technology (IJARMET), Volume 1, Issue 3, May 2017, Pages 36-43. ISSN: 2456-6446 (Online)

- [51] Mohammad Fasail PK, M.Pradeep, R.Sathishkumar, G.Ranjhitha, M.Valan Rajkumar, "Speed Control BLDC Motor using Fuzzy Logic and PID Controller fed Electric Vehicle", South Asian Journal of Engineering and Technology, Volume 3, Issue 3, March 2017, Pages 118-131. ISSN: 2454-9614 (Print)

- [52] Y. Hao, Z. Fang, Z. Yanjun, L. Yu, Z. Wenda, C. Wenjie, and L. Jinjun, "A Source-Current-Detected Shunt Active Power Filter Control Scheme Based on Vector Resonant Controller," Industry Applications, IEEE Transactions on, vol. 50, no. 3, pp. 1953-1965, 2014.

- [53] A. Nabae, I. Takahashi, and H. Akagi, "A New Neutral-Point-Clamped PWM Inverter," Industry Applications, IEEE Transactions on, vol. IA- 17, no. 5, pp. 518-523, 1981.

- [54] G.Vidhya Krishnan, M.Valan Rajkumar, D.Umakirthika, "Role of Internet of Things in Smart Passenger Cars", International Journal of Engineering And Computer Science (IJECS), Volume: 6, Issue: 5, May 2017, Pages 21410-21417. ISSN: 2319-7242 (Online).

- [55] M.Valan Rajkumar, T.Indumathi, "Performance Analysis of PV based Low Power Multi-Core Embedded Management using Wireless Communication System", International Journal of Emerging Technologies in Engineering Research (IJETER), Volume: 5, Issue: 5, May 2017, Pages 129-136. ISSN: 2454-6410 (Online).

- [56] C.Hemalatha, M.Valan Rajkumar, M.Gayathri, "Performance Analysis of IoT based Secured Smart Building Monitoring System Interface using GSM Technique", International Journal of Emerging Technologies in Engineering Research (IJETER), Volume: 5, Issue: 5, May 2017, Pages 141-147. ISSN: 2454-6410 (Online).

- [57] K. Ishaque, Z. Salam, H. Taheri, A. Shamsudin, "A critical evaluation of EA computational methods for Photovoltaic cell parameter extraction based on two diode model", Solar Energy, vol 85, pp.1768-1779,2011.

- [58] P.Pushparani, M.Valan Rajkumar, R.Suganya, "Simulation and Analysis of SVHM Technique for DCMLI under Transient Conditions with Non-Linear Loads", International Journal of Emerging Technologies in Engineering Research (IJETER), Volume: 5, Issue: 11, November 2017, Pages 90-96. ISSN: 2454-6410 (Online).

- [59] R.Suganya, M.Valan Rajkumar, P.Pushparani, "Simulation and Analysis of Boost Converter with MPPT for PV System using Chaos PSO Algorithm", International Journal of Emerging Technologies in Engineering Research (IJETER), Volume: 5, Issue: 11, November 2017, Pages 97-105. ISSN: 2454-6410 (Online).

- [60] P.Pushparani, M.Valan Rajkumar, R.Suganya, "Modeling and Analysis of Maximum Power Point Tracking for Photovoltaic System using Fuzzy Logic Controller", International Journal for Science and Advance Research in Technology (IJSART), Volume 3, Issue 11, November 2017, Pages 298-306. ISSN: 2395-1052 (Online)

- [61] R.Suganya, M.Valan Rajkumar, P.Pushparani, "Modeling and Analysis of Sinusoidal PWM Technique for CHB Multilevel Inverter for Photovoltaic System", International Journal for Science and Advance Research in Technology (IJSART), Volume 3, Issue 11, November 2017, Pages 307-315. ISSN: 2395-1052 (Online)

- [62] M.Sundaraperumal, M.Valan Rajkumar, D.Aravind, "Simulation and Analysis of APOD Pulse Width Modulation Technique for Z-Source Cascaded Multilevel Inverter for Photovoltaic System", International Journal for Science and Advance Research in Technology (IJSART), Volume 3, Issue 11, November 2017, Pages 816-824. ISSN: 2395-1052 (Online)

- [63] V.Mahesh, M.Valan Rajkumar, D.Aravind, "Improving Energy Efficiency based Aware Link Adaptation for Multiple-Input Multiple-Output OFDM Wireless Networks", International Journal of Recent Advancement in Engineering & Research (IJRAER), Volume 3, Issue 11, November 2017, Pages 18-27. ISSN: 2456-401X (Online)

- [64] S.Sathyaraj, D.Aravind, M.Valan Rajkumar, "Detection of Ventricular Fibrillation and Ventricular Tachycardia for Shockable Cardiac Arrhythmias using Slope Analysis Method", International Journal of Recent Advancement in Engineering & Research (IJRAER), Volume 3, Issue 11, November 2017, Pages 28-36. ISSN: 2456-401X (Online)

- [65] Z.Wang, J. Chen, M. Cheng, and K. T. Chau, "Field-oriented control and direct torque control for paralleled VSIs Fed PMSM drives with variable switching frequencies," IEEE Transactions on Power Electronics, vol. 31, no. 3, pp. 2417–2428, 2016.

International Journal of Computational Engineering Research (IJCER) is UGC approved Journal with Sl. No. 4627, Journal no. 47631.

K.Sridhar "Simulation and Analysis of Symmetric Seven-level CMLI using Multicarrier SPWM Technique with Reducing Number of Switches." International Journal of Computational Engineering Research (IJCER), vol. 7, no. 11, 2017, pp. 07-15.